# 3602A, 3622A FAMILY 3602, 3622 FAMILY 2048 BIT (512×4) HIGH SPEED PROM

|                          | 3602A-2<br>3622A-2 | 3602A<br>3622A | 3602<br>3622 |

|--------------------------|--------------------|----------------|--------------|

| Typ. T <sub>A</sub> (ns) | 45                 | 55             | 60           |

| Max. T <sub>A</sub> (ns) | 60                 | 70             | 70           |

- Low Power Dissipation --0.3mW/Bit

- Open Collector (3602A, 3602) or Three State (3622A, 3622) Outputs

- Simple Memory Expansion--Chip Select Input Lead

- Replaces Two 256×4 PROMs

Without Increasing Board

Area

- Polycrystalline Silicon Fuse

For Higher Reliability

- Hermetic 16-Pin DIP

The Intel® 3602A/3622A and 3602/3622 device families are 2048-bit bipolar PROMs organized as 512 words by 4 bits. The fast second generation 3602A/3622A joins its Intel predecessor, the 3602/3622, featuring 70 ns. A higher speed version, the 3602A-2/3622A-2, is now available at 60 ns. All 3602A/3622A specifications, except programming, are the same as the 3602/3622. Once programmed, the 3602A/3622A are interchangeable with the 3602/3622.

The PROMs are manufactured with all outputs initially logically high. Logic low levels can be electrically programmed in selected bit locations. Both open collector and three-state outputs are available. The power dissipation is typically 0.3 mW/bit.

The pin configuration of the PROMs is the same as the popular 1K bit,  $256 \times 4$  PROMs with the exception that CS<sub>2</sub> (pin 14) is address A<sub>8</sub>. The bit density of existing  $256 \times 4$  PROM systems can be easily doubled without an increase in area with the 3602A/3622A or 3602/3622. These PROMs, like the  $256 \times 4$  PROMs, are in 16-pin dual in-line package.

A pin compatible, mask programmable 3302/3322 ROM is available for large volume production systems initially using the 3602/3622. Please contact Intel directly for details on these ROMs.

###

#### **PROGRAMMING**

The programming specifications are described in the PROM/ROM Programming Instructions on page 3-55.

## **Absolute Maximum Ratings\***

| Temperature Under Bias    | -65°C to +125°C |

|---------------------------|-----------------|

| Storage Temperature       | -65°C to +160°C |

| Output or Supply Voltages |                 |

| All Input Voltages        |                 |

|                           | 100mA           |

#### \*COMMENT

Stresses above those listed under "Absolute Maximum Rating" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or at any other condition above those indicated in the operational sections of this specification is not implied.

### **D. C. Characteristics:** All Limits Apply for $V_{CC}$ = +5.0V ±5%, $T_A$ = 0°C to +75°C

|                  |                                      | Limits |                              |       |      |                                                              |  |

|------------------|--------------------------------------|--------|------------------------------|-------|------|--------------------------------------------------------------|--|

| Symbol           | Parameter                            | Min.   | in. Typ. <sup>[1]</sup> Max. |       | Unit | Test Conditions                                              |  |

| I <sub>FA</sub>  | Address Input Load Current           |        | -0.05                        | -0.25 | mA   | $V_{CC} = 5.25V, V_A = 0.45V$                                |  |

| I <sub>FS</sub>  | Chip Select Input Load Current       |        | -0.05                        | -0.25 | mA   | $V_{CC} = 5.25V, V_{S} = 0.45V$                              |  |

| I <sub>RA</sub>  | Address Input Leakage Current        |        |                              | 40    | μΑ   | V <sub>CC</sub> = 5.25V, V <sub>A</sub> = 5.25V              |  |

| IRS              | Chip Select Input Leakage<br>Current |        |                              | 40    | μΑ   | $V_{CC} = 5.25 \text{V}, V_{S} = 5.25 \text{V}$              |  |

| V <sub>CA</sub>  | Address Input Clamp Voltage          |        | -0.9                         | -1.5  | V    | $V_{CC} = 4.75V, I_A = -10mA$                                |  |

| V <sub>CS</sub>  | Chip Select Input Clamp<br>Voltage   |        | -0.9                         | -1.5  | ٧    | V <sub>CC</sub> = 4.75V, I <sub>S</sub> = -10mA              |  |

| V <sub>OL</sub>  | Output Low Voltage                   |        | 0.3                          | 0.45  | V    | V <sub>CC</sub> = 4.75V, I <sub>OL</sub> = 15mA              |  |

| I <sub>CEX</sub> | Output Leakage Current               |        |                              | 40    | μΑ   | V <sub>CC</sub> = 5.25V, V <sub>CE</sub> = 5.25V             |  |

| lcc              | Power Supply Current                 |        | 110                          | 140   | mA   | $\frac{V_{CC}}{CS}$ =5.25V, $V_{A0} \rightarrow V_{A8}$ = 0V |  |

| VIL              | Input "Low" Voltage                  |        | <u> </u>                     | 0.85  | V    | V <sub>CC</sub> = 5.0V                                       |  |

| V <sub>IH</sub>  | Input "High" Voltage                 | 2.0    |                              |       | V    | V <sub>CC</sub> = 5.0V                                       |  |

#### 3622A, 3622A-2, 3622 ONLY

| Symbol              | Parameter                                  | Min. | Typ.[1] | Max. | Unit | Test Conditions                                                                |

|---------------------|--------------------------------------------|------|---------|------|------|--------------------------------------------------------------------------------|

| llol                | Output Leakage for High<br>Impedance Stage |      |         | 40   | μΑ   | V <sub>O</sub> =5.25V or 0.45V,<br>V <sub>CC</sub> =5.25V, <del>CS</del> =2.4V |

| 1 <sub>SC</sub> [2] | Output Short Circuit Current               | -15  | -25     | -60  | mA   | V <sub>CC</sub> =5.00V, T <sub>A</sub> =25°C,<br>V <sub>O</sub> = 0V           |

| V <sub>OH</sub>     | Output High Voltage                        | 2.4  |         |      | V    | I <sub>OH</sub> = -2.4mA, V <sub>CC</sub> = 4.75V                              |

NOTES: 1. Typical values are at 25°C and at nominal voltage.

<sup>2.</sup> Unmeasured outputs are open during this test.

### A. C. Characteristics $V_{CC} = +5V \pm 5\%$ , $T_A = 0$ °C to +75°C

|                                   |                             | 1                  | ЛАХ. LIMIT     | •            | UNIT |                                         |  |

|-----------------------------------|-----------------------------|--------------------|----------------|--------------|------|-----------------------------------------|--|

| SYMBOL                            | PARAMETER                   | 3602A-2<br>3622A-2 | 3602A<br>3622A | 3602<br>3622 |      | CONDITIONS                              |  |

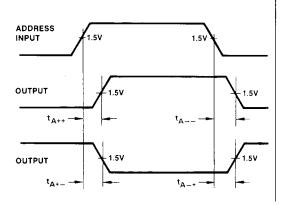

| t <sub>A++</sub> , t <sub>A</sub> | Address to Output Delay     | 60                 | 70             | 70           | ns   |                                         |  |

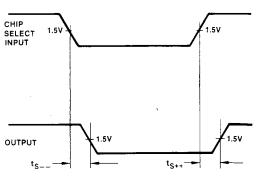

| t <sub>S++</sub>                  | Chip Select to Output Delay | 30                 | 30             | 30           | ns   | CS = V <sub>IL</sub> to Select the PROM |  |

| t <sub>S</sub>                    | Chip Select to Output Delay | 30                 | 30             | 30           | ns   |                                         |  |

### Capacitance (1) TA = 25°C, f = 1 MHz

| SYMBOL           | DADAMETER                     | LIMITS |      | LINIT | TEST CONDITIONS      |                         |  |

|------------------|-------------------------------|--------|------|-------|----------------------|-------------------------|--|

|                  | PARAMETER                     | TYP.   | MAX. | UNIT  | TEST CONDITIONS      |                         |  |

| CINA             | Address Input Capacitance     | 4      | 10   | pF    | V <sub>CC</sub> = 5V | `V <sub>IN</sub> = 2.5V |  |

| C <sub>INS</sub> | Chip-Select Input Capacitance | 6      | 10   | pF    | V <sub>CC</sub> = 5V | V <sub>IN</sub> = 2.5V  |  |

| C <sub>OUT</sub> | Output Capacitance            | 7      | 12   | pF    | V <sub>CC</sub> = 5V | V <sub>OUT</sub> = 2.5V |  |

NOTE 1: This parameter is only periodically sampled and is not 100% tested.

## **Switching Characteristics**

# Conditions of Test:

Input pulse amplitudes - 2.5V

Input pulse rise and fall times of

5 nanoseconds between 1 volt and 2 volts

Speed measurements are made at 1.5 volt levels

Output loading is 15 mA and 30 pF

15 mA TEST LOAD

VCC

300Ω

300Ω

600Ω

#### Waveforms

#### ADDRESS TO OUTPUT DELAY

Frequency of test - 2.5 MHz

#### CHIP SELECT TO OUTPUT DELAY