# intel

# Schottky Bipolar 8212

# **EIGHT-BIT INPUT/OUTPUT PORT**

- Fully Parallel 8-Bit Data Register and Buffer

- Service Request Flip-Flop for Interrupt Generation

- Low Input Load Current .25 mA Max.

- Three State Outputs

- Outputs Sink 15 mA

- 3.65V Output High Voltage for Direct Interface to 8080 CPU or 8008 CPU

- Asynchronous Register Clear

- Replaces Buffers, Latches and Multiplexers in Microcomputer Systems

- Reduces System Package Count

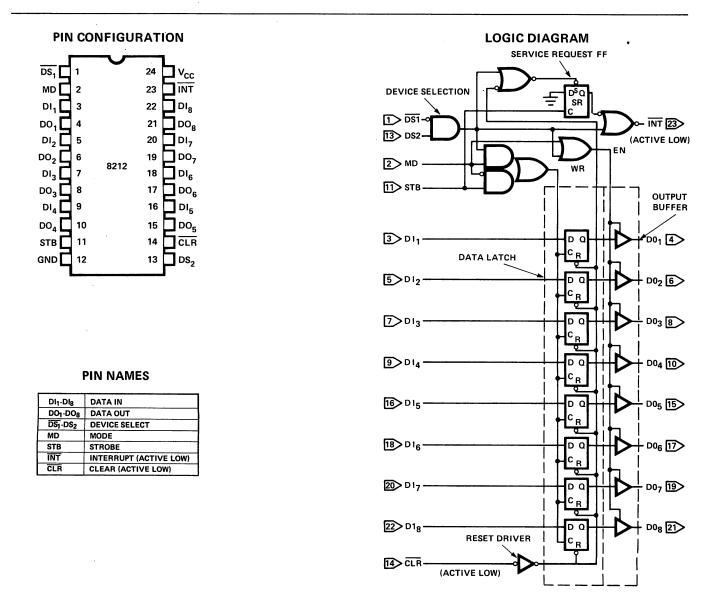

The 8212 input/output port consists of an 8-bit latch with 3-state output buffers along with control and device selection logic. Also included is a service request flip-flop for the generation and control of interrupts to the microprocessor.

The device is multimode in nature. It can be used to implement latches, gated buffers or multiplexers. Thus, all of the principal peripheral and input/output functions of a microcomputer system can be implemented with this device.

## **Functional Description**

#### **Data Latch**

The 8 flip-flops that make up the data latch are of a "D" type design. The output (Q) of the flip-flop will follow the data input (D) while the clock input (C) is high. Latching will occur when the clock (C) returns low.

The data latch is cleared by an asynchronous reset input ( $\overline{CLR}$ ). (Note: Clock (C) Overides Reset ( $\overline{CLR}$ ).)

#### **Output Buffer**

The outputs of the data latch (Q) are connected to 3-state, non-inverting output buffers. These buffers have a common control line (EN); this control line either enables the buffer to transmit the data from the outputs of the data latch (Q) or disables the buffer; forcing the output into a high impedance state. (3-state)

This high-impedance state allows the designer to connect the 8212 directly onto the microprocessor bi-directional data bus.

#### **Control Logic**

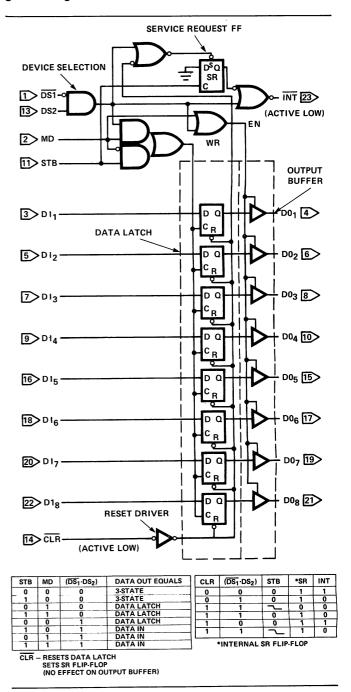

The 8212 has control inputs DS1, DS2, MD and STB. These inputs are used to control device selection, data latching, output buffer state and service request flip-flop.

#### **DS1**, DS2 (Device Select)

These 2 inputs are used for device selection. When  $\overline{\text{DS1}}$  is low and DS2 is high ( $\overline{\text{DS1}} \cdot \text{DS2}$ ) the device is selected. In the selected state the output buffer is enabled and the service request flip-flop (SR) is asynchronously set.

#### MD (Mode)

This input is used to control the state of the output buffer and to determine the source of the clock input (C) to the data latch.

When MD is high (output mode) the output buffers are enabled and the source of clock (C) to the data latch is from the device selection logic ( $\overline{DS1} \cdot DS2$ ). When MD is low (input mode) the output buffer state is determined by the device selection logic ( $\overline{DS1} \cdot$ DS2) and the source of clock (C) to the data latch is the STB (Strobe) input.

#### STB (Strobe)

This input is used as the clock (C) to the data latch for the input mode MD = 0) and to synchronously reset the service request flip-flop (SR).

Note that the SR flip-flop is negative edge triggered.

#### Service Request Flip-Flop

The (SR) flip-flop is used to generate and control interrupts in microcomputer systems. It is asynchronously set by the  $\overline{\text{CLR}}$  input (active low). When the (SR) flip-flop is set it is in the non-interrupting state.

The output of the (SR) flip-flop (Q) is connected to an inverting input of a "NOR" gate. The other input to the "NOR" gate is non-inverting and is connected to the device selection logic ( $\overline{DS1} \cdot DS2$ ). The output of the "NOR" gate ( $\overline{INT}$ ) is active low (interrupting state) for connection to active low input priority generating circuits.

# Applications Of The 8212 -- For Microcomputer Systems

- I Basic Schematic Symbol

- II Gated Buffer

- III Bi-Directional Bus Driver

- IV Interrupting Input Port

- V Interrupt Instruction Port

- VI Output Port

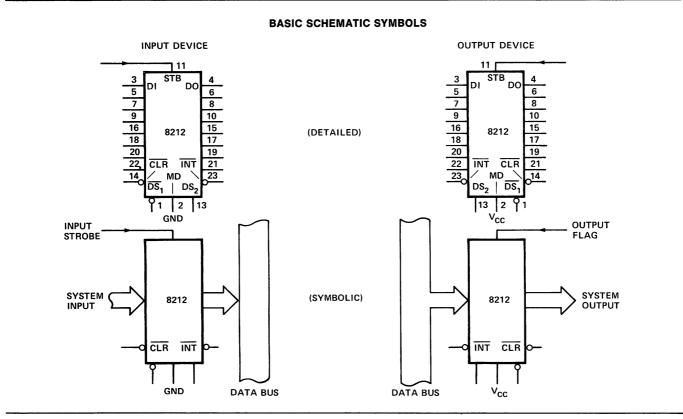

# I. Basic Schematic Symbols

Two examples of ways to draw the 8212 on system schematics—(1) the top being the detailed view showing pin numbers, and (2) the bottom being the symbolic view showing the system input or output

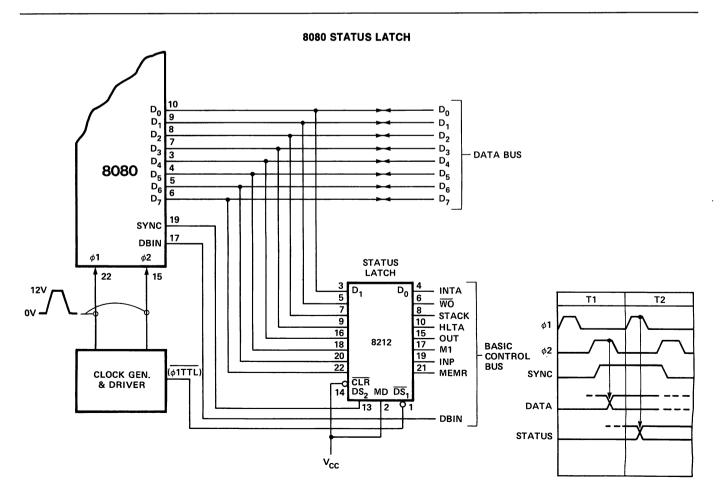

- VII 8080 Status Latch

- VIII 8008 System

- IX 8080 System:

- 8 Input Ports

- 8 Output Ports

- 8 Level Priority Interrupt

as a system bus (bus containing 8 parallel lines). The output to the data bus is symbolic in referencing 8 parallel lines.

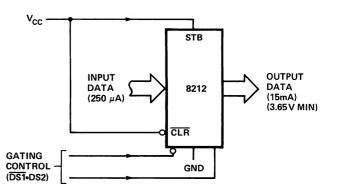

# II. Gated Buffer (3 - STATE)

The simplest use of the 8212 is that of a gated buffer. By tying the mode signal low and the strobe input high, the data latch is acting as a straight through gate. The output buffers are then enabled from the device selection logic  $\overline{\text{DS1}}$  and DS2.

When the device selection logic is false, the outputs are 3-state.

When the device selection logic is true, the input data from the system is directly transferred to the output. The input data load is 250 micro amps. The output data can sink 15 milli amps. The minimum high output is 3.65 volts.

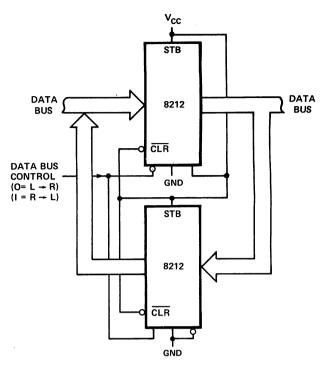

#### **III. Bi-Directional Bus Driver**

A pair of 8212's wired (back-to-back) can be used as a symmetrical drive, bi-directional bus driver. The devices are controlled by the data bus input control which is connected to  $\overline{DS1}$  on the first 8212 and to DS2 on the second. One device is active, and acting as a straight through buffer the other is in 3-state mode. This is a very useful circuit in small system design.

**BI-DIRECTIONAL BUS DRIVER**

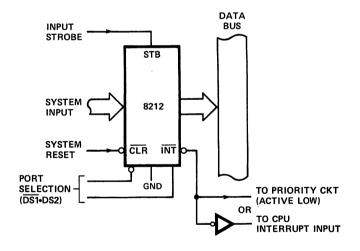

#### **IV. Interrupting Input Port**

This use of an 8212 is that of a system input port that accepts a strobe from the system input source, which in turn clears the service request flip-flop and interrupts the processor. The processor then goes through a service routine, identifies the port, and causes the device selection logic to go true enabling the system input data onto the data bus.

**INTERRUPTING INPUT PORT**

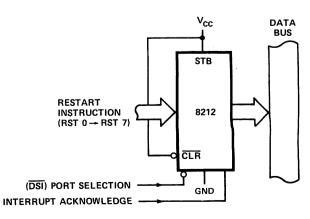

#### **V. Interrupt Instruction Port**

The 8212 can be used to gate the interrupt instruction, normally RESTART instructions, onto the data bus. The device is enabled from the interrupt acknowledge signal from the microprocessor and from a port selection signal. This signal is normally tied to ground. ( $\overline{DS1}$  could be used to multiplex a variety of interrupt instruction ports onto a common bus).

INTERRUPT INSTRUCTION PORT

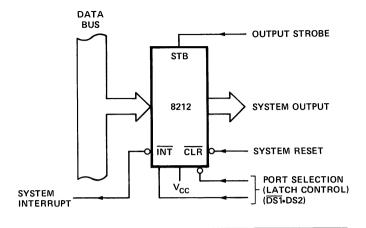

# VI. Output Port (With Hand-Shaking)

The 8212 can be used to transmit data from the data bus to a system output. The output strobe could be a hand-shaking signal such as "reception of data" from the device that the system is outputting to. It in turn, can interrupt the system signifying the reception of data. The selection of the port comes from the device selection logic. ( $\overline{DS1} \cdot DS2$ )

**OUTPUT PORT (WITH HAND-SHAKING)**

# VII. 8080 Status Latch

Here the 8212 is used as the status latch for an 8080 microcomputer system. The input to the 8212 latch is directly from the 8080 data bus. Timing shows that when the SYNC signal is true, which is connected to the DS2 input and the phase 1 signal is true, which is a TTL level coming from the clock generator; then, the status data will be latched into the 8212.

Note: The mode signal is tied high so that the output on the latch is active and enabled all the time. It is shown that the two areas of concern are the bidirectional data bus of the microprocessor and the control bus.

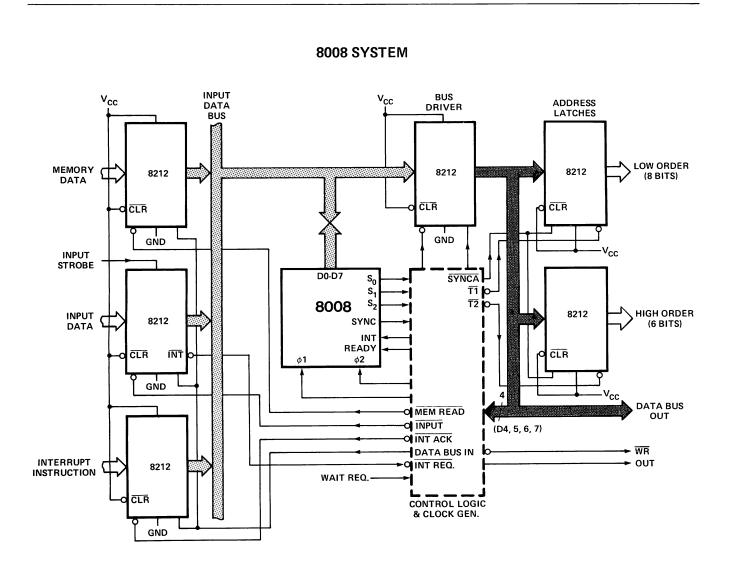

# VIII. 8008 System

This shows the 8212 used in an 8008 microcomputer system. They are used to multiplex the data from three different sources onto the 8008 input data bus. The three sources of data are: memory data, input data, and the interrupt instruction. The 8212 is also used as the uni-directional bus driver to provide a proper drive to the address latches (both low order and high order are also 8212's) and to provide adequate drive to the output data bus. The control of these six 8212's in the 8008 system is provided by the control logic and clock generator circuits. These circuits consist of flip-flops, decoders, and gates to generate the control functions necessary for 8008 microcomputer systems. Also note that the input data port has a strobe input. This allows the processor to be interrupted from the input port directly. The control of the input bus consists of the data bus input signal, control logic, and the appropriate status signal for bus discipline whether memory read, input, or interrupt acknowledge. The combination of these four signals determines which one of these three devices will have access to the input data bus. The bus driver, which is implemented in an 8212, is also controlled by the control logic and clock generator so it can be 3-stated when necessary and also as a control transmission device to the address latches. Note: The address latches can be 3-stated for DMA purposes and they provide 15 milli amps drive, sufficient for large bus systems.

5-106

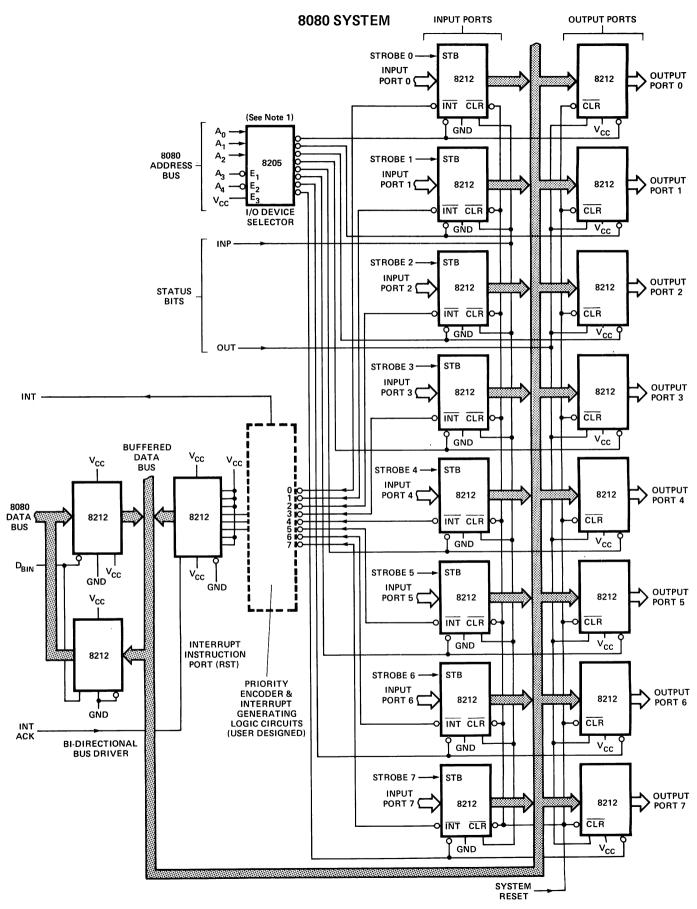

## IX. 8080 System

This drawing shows the 8212 used in the I/O section of an 8080 microcomputer system. The system consists of 8 input ports, 8 output ports, 8 level priority systems, and a bidirectional bus driver. (The data bus within the system is darkened for emphasis). Basically, the operation would be as follows: The 8 ports, for example, could be connected to 8 keyboards, each keyboard having its own priority level. The keyboard could provide a strobe input of its own which would clear the service request flip-flop. The INT signals are connected to an 8 level priority encoding circuit. This circuit provides a positive true level to the central processor (INT) along with a three-bit code to the interrupt instruction port for the generation of RESTART instructions. Once the processor has been interrupted and it acknowledges the reception of the interrupt, the Interrupt Acknowledge signal is generated. This signal transfers data in the form of a RESTART instruction onto the buffered data bus. When the DBIN signal is true this RESTART instruction is gated into the microcomputer, in this case, the 8080 CPU. The 8080 then performs a software controlled interrupt service routine, saving the status of its current operation in the push-down stack and performing an INPUT instruction. The INPUT instruction thus sets the INP status

bit, which is common to all input ports.

Also present is the address of the device on the 8080 address bus which in this system is connected to an 8205, one out of eight decoder with active low outputs. These active low outputs will enable one of the input ports, the one that interrupted the processor, to put its data onto the buffered data bus to be transmitted to the CPU when the data bus input signal is true. The processor can also output data from the 8080 data bus to the buffered data bus when the data bus input signal is false. Using the same address selection technique from the 8205 decoder and the output status bit, we can select with this system one of eight output ports to transmit the data to the system's output device structure.

Note: This basic I/O configuration for the 8080 can be expanded to 256 input devices and 256 output devices all using 8212 and, of course, the appropriate decoding.

Note that the 8080 is a 3.3-volt minimum high input requirement and that the 8212 has a 3.65-volt minimum high output providing the designer with a 350 milli volt noise margin worst case for 8080 systems when using the 8212.

# **SCHOTTKY BIPOLAR 8212**

Note 1. This basic I/O configuration for the 8080 can be expanded to 256 input devices and 256 output devices all using 8212 and the appropriate decoding.

# Absolute Maximum Ratings\*

| Temperature Under Bias Plastic65°C to +75°C               |

|-----------------------------------------------------------|

| Storage Temperature65°C to +160°C                         |

| All Output or Supply Voltages $\ldots -0.5$ to $+7$ Volts |

| All Input Voltages 1.0 to 5.5 Volts                       |

| Output Currents125 mA                                     |

\*COMMENT: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or at any other condition above those indicated in the operational sections of this specification is not implied.

# **D.C. Characteristics**

$T_A = 0^{\circ}C \text{ to } +75^{\circ}C \quad V_{CC} = +5V \pm 5\%$

| Symbol                | Parameter                                                                                |      | Limits |      | Unit | Test Conditions                |

|-----------------------|------------------------------------------------------------------------------------------|------|--------|------|------|--------------------------------|

|                       |                                                                                          | Min. | Тур.   | Max. |      |                                |

| F                     | Input Load Current<br>ACK, DS <sub>2</sub> , CR, DI <sub>1</sub> -DI <sub>8</sub> Inputs |      |        | 25   | mA   | $V_F = .45V$                   |

| IF                    | Input Load Current<br>MD Input                                                           |      |        | 75   | mA   | $V_F = .45V$                   |

| I <sub>F</sub>        | Input Load Current<br>DS <sub>1</sub> Input                                              |      |        | -1.0 | mA   | $V_F = .45V$                   |

| I <sub>R</sub>        | Input Leakage Current<br>ACK, DS, CR, DI₁-DI₃ Inputs                                     |      |        | 10   | μΑ   | $V_R = 5.25V$                  |

| I <sub>R</sub>        | Input Leakage Current<br>MO Input                                                        |      |        | 30   | μΑ   | $V_{R} = 5.25V$                |

| I <sub>R</sub>        | Input Leakage Current<br>DS <sub>1</sub> Input                                           |      |        | 40   | μΑ   | $V_{R} = 5.25V$                |

| Vc                    | Input Forward Voltage Clamp                                                              |      |        | -1   | V    | $I_c = -5 \text{ mA}$          |

| VIL                   | Input "Low" Voltage                                                                      |      |        | .85  | V    |                                |

| VIH                   | Input "High" Voltage                                                                     | 2.0  |        |      | V    |                                |

|                       | Output "Low" Voltage                                                                     |      |        | .45  | V    | $I_{OL} = 15 \text{ mA}$       |

| V <sub>OH</sub>       | Output "High" Voltage                                                                    | 3.65 | 4.0    |      | V    | $I_{O\dot{H}} = -1 \text{ mA}$ |

| I <sub>sc</sub>       | Short Circuit Output Current                                                             | -15  |        | -75  | mA   | $V_{\circ} = 0 V$              |

| <b>I</b> <sub>0</sub> | Output Leakage Current<br>High Impedance State                                           |      |        | 20   | μΑ   | $V_{\odot} = .45V/5.25V$       |

| I <sub>cc</sub>       | Power Supply Current                                                                     |      | 90     | 130  | mA   |                                |

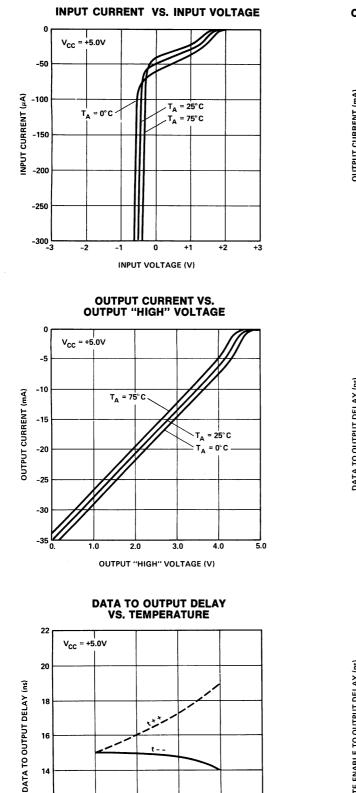

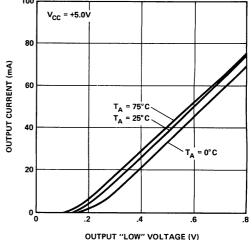

# **Typical Characteristics**

14

12

10 └ -25

0

25

50

TEMPERATURE (°C)

75

**OUTPUT CURRENT VS. OUTPUT "LOW" VOLTAGE** 100

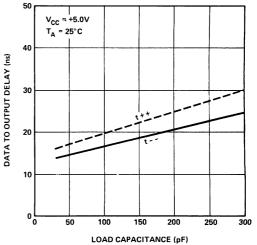

DATA TO OUTPUT DELAY **VS. LOAD CAPACITANCE**

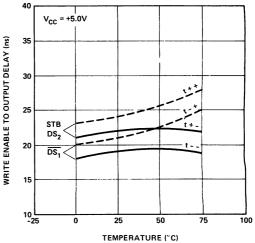

WRITE ENABLE TO OUTPUT DELAY VS. TEMPERATURE

100

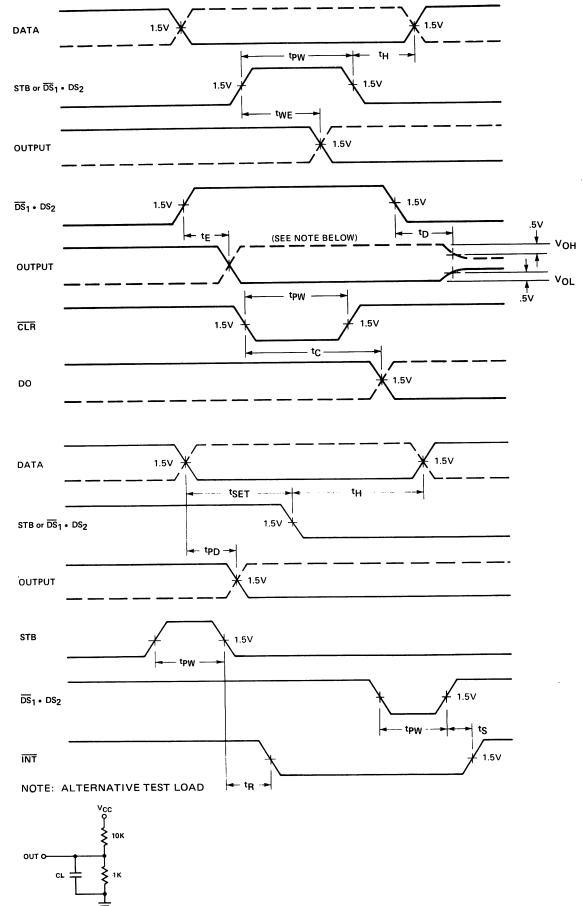

# **Timing Diagram**

# A.C. Characteristics

$T_{A} = 0^{\circ}C \text{ to } +75^{\circ}C$   $V_{CC} = +5V \pm 5\%$

| Symbol           | Parameter                    |      | Limits |      | Unit | Test Conditions |

|------------------|------------------------------|------|--------|------|------|-----------------|

|                  |                              | Min. | Тур.   | Max. |      |                 |

| t <sub>pw</sub>  | Pulse Width                  | 30   |        |      | ns   |                 |

| t <sub>pd</sub>  | Data To Output Delay         |      |        | 30   | ns   |                 |

| t <sub>we</sub>  | Write Enable To Output Delay | -    |        | 40   | ns   |                 |

| t <sub>set</sub> | Data Setup Time              | 15   |        |      | ns   |                 |

| t <sub>h</sub>   | Data Hold Time               | 20   |        |      | ns   |                 |

| t,               | Reset To Output Delay        |      |        | 40   | ns   |                 |

| t <sub>s</sub>   | Set To Output Delay          |      |        | 30   | ns   |                 |

| e                | Output Enable/Disable Time   |      |        | 45   | ns   |                 |

| t <sub>c</sub>   | Clear To Output Delay        |      |        | 55   | ns   |                 |

# $\label{eq:capacity} \textbf{CAPACITANCE}^{\,*} \quad \textbf{F} = 1 \ \textbf{MHz} \quad \textbf{V}_{\text{BIAS}} = 2.5 \textbf{V} \quad \textbf{V}_{\text{CC}} = +5 \textbf{V} \quad \textbf{T}_{\text{A}} = 25^{\circ} \textbf{C}$

| Symbol          | Test                                       | LIN  | LIMITS |  |  |

|-----------------|--------------------------------------------|------|--------|--|--|

|                 |                                            | Тур. | Max.   |  |  |

| C <sub>IN</sub> | DS <sub>1</sub> MD Input Capacitance       | 9 pF | 12 pF  |  |  |

| C <sub>IN</sub> | DS₂, CK, ACK, DI₁-DI₀<br>Input Capacitance | 5 pF | 9 pF   |  |  |

| COUT            | DO1-DO8 Output Capacitance                 | 8 pF | 12 pF  |  |  |

\*This parameter is sampled and not 100% tested.

# **Switching Characteristics**

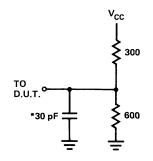

CONDITIONS OF TEST Input Pulse Amplitude = 2.5 V Input Rise and Fall Times 5 ns Between 1V and 2V Measurements made at 1.5V with 15 mA & 30 pF Test Load

15mA & 30pF

\* INCLUDING JIG & PROBE CAPACITANCE