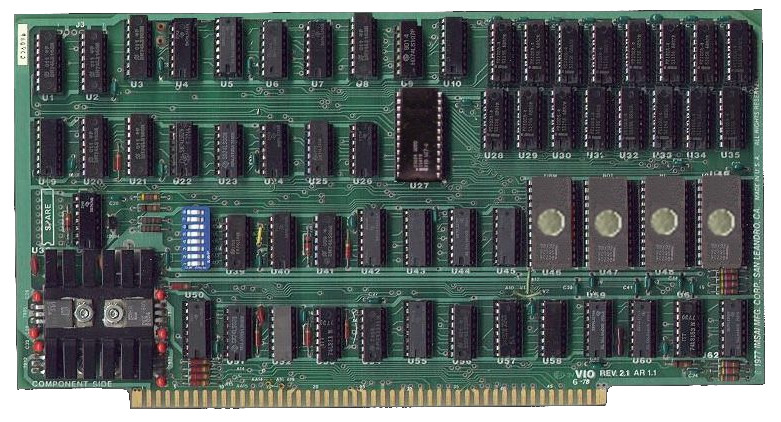

VIO (Discontinued)

The VIO is a single board memory mapped video board designed to drive monochrome CRT displays.

The board has been discontinued from production due to the lack of available parts (i3624/74S474 512×8 Bipolar PROM,

2102-type 1K×1 SRAM) and compatible working CRT displays.

Although you cannot purchase a new VIO, this page contains support information including errata

(some has never been published before), programmed parts hex files, the complete manual in .pdf format,

and user enhancements and modifications.

There are two VIO revisions in circulation, VIO-C and VIO-D.

The VIO-D (pictured) has a 7-pin connector at the top-left of the board that outputs TTL sync and composite video.

The VIO-C (click the ⏭ button) outputs composite video only. The VIO has 2 KB of firmware ROM and 2 KB of video RAM.

By default, this 4 KB block is positioned in the address space F000 through FFFF.

By adding a documented jumper, the 1 MB address space FF000 through FFFFF may be used.

Resources

Schematics

The schematics listed here were initially scanned by Herb Johnson.

You should check out his IMSAI collection at

https://www.retrotechnology.com/herbs_stuff/d_imsai.html.

The corrections and markups were done by Robert E. Weatherford.

Manuals

Setup

If you are moving a VIO into a new system, you should take the time to make sure it is set up properly based on your system’s hardware and software.

Address Map

The VIO decodes up to 20 address bits, may be configured to occupy 2K or 4K of memory space in 4K increments starting at

x000, x800, Fx000, or Fx800. The VIO does not use any I/O ports.

Jumper Areas

The VIO has several jumper areas on the board that must be properly configured. Pay particular attention to jumper F.

| Jumpers |

Description |

| A and B |

The A and B jumper pads are between U39 and U40 and is provided to optimize the address latch timing between the MPU-A and MPU-B.

Jumper A to PH for an 8080 CPU or B to PH for an 8085 CPU.

Because the VIO may be used with other processors, it is probably worth going into more technical detail as to what this jumper does.

Refer to the top-center of the IMSAI VIO Schematic where the pSYNC and Φ1 are NANDed.

Jumpering PH to A latches the state of the address lines on the rising edge of Φ1 which is 90ns after the address lines are stable

(not counting delays in the MPU-A and the VIO).

For the MPU-B, the Φ1 is actually the inverted Φ2 (8085 clock) signal.

The pSYNC signal is the 8085 ALE signal, and the addresses are not guaranteed to be stable until the clock rises

(the generated Φ1 falls). This means that you must latch the addresses on the falling edge of pSYNC • Φ1.

If you want to be strictly IEEE 696 compliant, jumper PH to B.

This will latch the address on the falling edge of pSTVAL* (which is Φ1 on the VIO schematic).

The address bus is not stable on the rising edge.

Even if you are running with an MPU-A, jumpering this way will only delay the address latching by 60ns.

|

| C and D |

The C and D jumpers are relevant only if you have an IMSAI IMM running in your system. |

| F |

The F jumper is located near S-100 bus pin 15 and is used to assert the PHANTOM* signal on the S-100 bus to disable system RAM

when the VIO is being addressed. If you have 64K or more of RAM in your system, you will need to do something with this jumper.

Otherwise, you will have both your RAM and the VIO driving the data in bus at the same time. On IMSAI systems,

A16 and A19 are typically used as a PHANTOM line, which is why those are the two jumper options.

For an IEEE 696 compliant system, pad F should be jumpered to A19, which is the IEEE 696 PHANTOM*, pin 67.

|

| M |

The M jumper is located between U53 and U54 on the board.

If your system is a 1 MB system (drives 20 address lines), you can use the M jumper to place the VIO in the top 64K page.

If your system is a 16 MB system (drives all 24 address lines), the M jumper will cause the VIO to appear in every 16th 64K page starting at page zero. |

DIP Switches

See the DIP switch descriptions below. For IMDOS and CP/M 2.2 and above, the standard settings from switch 1 through 8 are: off, off, off, off, off, ON, off, off.

| Switch |

Description |

| 1 thru 4 |

Set the base address. Switch 1 through 4 determines the state for address bits A12, A13, A14, and A15 respectively. ON equals 0 and OFF equals 1. The default is all OFF, setting the base address to F000. |

| 5 |

Determines whether the VIOROM is in the upper 2K of the VIO address space.

If the switch is ON, the VIOROM resides in the upper 2K and the VIO RAM is in the lower 2K;

otherwise, the VIOROM resides in the lower 2K and the VIO RAM resides in the upper 2K.

The default is OFF, placing the VIOROM at F800 and the VIO RAM at F000. |

| 6 |

Determines whether the VIOROM is active.

If the switch is ON, the VIOROM is active at the address range specified by switch 5;

otherwise, the VIOROM is disabled, and the VIO only occupies 2K in the system for the VIO RAM. The default in ON. |

| 7 |

Determines whether a one-cycle wait state is enabled on all VIOROM and VIO RAM accesses.

Be advised that if your bus masters do not drive the legacy PWAIT signal (bus pin 27),

the wait state generator will not function. |

| 8 |

Not used. |

Programmed Part Images

The VIO uses several programmed parts. All of the images are available here in Intel Hex format.

VIORAM Map (U27)

The VIORAM map is stored in a 512×8 bipolar PROM which maps the character and line positions into RAM addresses.

Most any available 512×8 24-pin DIP 3-State part that is pin compatible with the 74S474 will do,

which makes finding a match with a bipolar PROM programmer easier.

Most browsers will not display hex files. Use the browser’s Save link as... to download them.

Firmware (U46)

The original firmware was 1KB in size and was stored in a 2708 EPROM. Later production switched to a 2KB image in a 2716 EPROM.

This one is the later 2K version.

Most browsers will not display hex files. Use the browser’s Save link as... to download them.

Character Generators (U47, U48, and U49)

These files are for U47, U48, and U49. They are 1 KB in size so they will fit in a 2708, or in one half a 2716.

To construct a dual-generator 2716, load the lower set file in the lower 1 KB and the upper set in the upper 1 KB.

You can, of course, load the same one in both halves.

Standard VIO (5×7)

These are the original IMSAI VIO character generators.

Most browsers will not display hex files. Use the browser’s Save link as... to download them.

Datasheets

Errata

Various errors in the documentation and the PC layout are documented here.

PCB Layout Errors

- The AA14 and AA15 signals are connected to the wrong S-100 bus pins.

AA14 is supposed to be on pin 13, but it is on pin 63. AA15 is supposed to be on pin 14, but it is on pin 64.

AA14 and AA15 were never used outside the IMM (Intelligent Memory Manager, enabler of the “Megabyte Micro”).

Bus pins 63 and 64 were never used by IMSAI, but they are extended address lines A22 and A23 under the IEEE 696 standard.

This may be why this error was never discovered.

|